# IMP811, IMP812

**POWER MANAGEMENT**

# 4-Pin µP Voltage Supervisor with Manual Reset

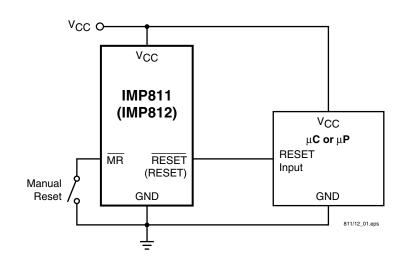

The IMP811/IMP812 are low-power supervisors designed to monitor voltage levels of 3.0V, 3.3V and 5.0V power supplies in low-power microprocessor ( $\mu$ P), microcontroller ( $\mu$ C) and digital systems. Each features a debounced manual reset input. The IMP811/812 are improved drop-in replacements for the Maxim MAX811/812 with extended temperature specifications to 105°C.

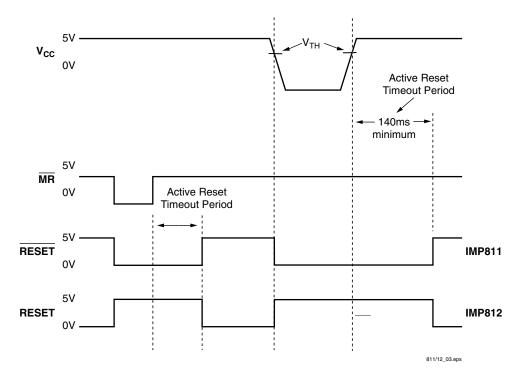

A reset signal is issued if the power supply voltage drops below a preset threshold and is asserted for at least 140ms after the supply has risen above the reset threshold. The IMP811 has an active-low output  $\overline{\text{RESET}}$  that is guaranteed to be in the correct state for  $V_{CC}$  down to 1.1V. The IMP812 has an active-high output RESET. The reset comparator is designed to ignore fast transients on  $V_{CC}$ .

Low power consumption makes the IMP811/IMP812 ideal for use in portable and battery-operated equipment. Available in a compact 4-pin SOT143 package, the devices use minimal board space.

Six voltage thresholds are available to support 3V to 5V systems:

| <b>Reset Threshold</b> |             |  |

|------------------------|-------------|--|

| Suffix                 | Voltage (V) |  |

| L                      | 4.63        |  |

| М                      | 4.38        |  |

| J                      | 4.00        |  |

| Т                      | 3.08        |  |

| S                      | 2.93        |  |

| R                      | 2.63        |  |

#### **Block Diagrams**

#### **Key Features**

- Improved Maxim MAX811/MAX812 replacement

Specified to 105°C

- New 4.0V threshold option

- ♦ 6µA supply current

- Monitor 5V, 3.3V and 3V supplies

- Manual reset input

- ◆ 140ms min. reset pulse width

- Guaranteed over temperature

- Active-LOW reset valid with 1.1V supply (IMP811)

- Small 4-pin SOT-143 package

- No external components

- Power-supply transient-immune design

### **Applications**

- Computers and controllers

- Embedded controllers

- Battery operated systems

- Intelligent instruments

- Wireless communication systems

- PDAs and handheld equipment

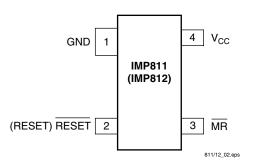

# **Pin Configuration**

#### SOT143

# **Ordering Information**

| Part Number <sup>1</sup>                              | Reset Threshold (V)                                  | Temperature Range | Pin-Package | Package Marking <sup>2</sup><br>(XX Lot Code) |  |  |

|-------------------------------------------------------|------------------------------------------------------|-------------------|-------------|-----------------------------------------------|--|--|

| IMP811 Active LOW Res                                 | IMP811 Active LOW Reset with Active LOW Manual Reset |                   |             |                                               |  |  |

| IMP811LEUS-T                                          | 4.63                                                 | -40°C to +105°C   | 4-SOT143    | AMXX                                          |  |  |

| IMP811MEUS-T                                          | 4.38                                                 | -40°C to +105°C   | 4-SOT143    | ANXX                                          |  |  |

| IMP811JEUS-T                                          | 4.00                                                 | -40°C to +105°C   | 4-SOT143    | AOXX                                          |  |  |

| IMP811TEUS-T                                          | 3.08                                                 | -40°C to +105°C   | 4-SOT143    | APXX                                          |  |  |

| IMP811SEUS-T                                          | 2.93                                                 | -40°C to +105°C   | 4-SOT143    | AQXX                                          |  |  |

| IMP811REUS-T                                          | 2.63                                                 | -40°C to +105°C   | 4-SOT143    | ARXX                                          |  |  |

| IMP812 Active HIGH Reset with Active LOW Manual Reset |                                                      |                   |             |                                               |  |  |

| IMP812LEUS-T                                          | 4.63                                                 | -40°C to +105°C   | 4-SOT143    | ASXX                                          |  |  |

| IMP812MEUS-T                                          | 4.38                                                 | -40°C to +105°C   | 4-SOT143    | ATXX                                          |  |  |

| IMP812JEUS-T                                          | 4.00                                                 | -40°C to +105°C   | 4-SOT143    | AUXX                                          |  |  |

| IMP812TEUS-T                                          | 3.08                                                 | -40°C to +105°C   | 4-SOT143    | AVXX                                          |  |  |

| IMP812SEUS-T                                          | 2.93                                                 | -40°C to +105°C   | 4-SOT143    | AWXX                                          |  |  |

| IMP812REUS-T                                          | 2.63                                                 | -40°C to +105°C   | 4-SOT143    | AXXX                                          |  |  |

Notes: 1. Tape and Reel packaging is indicated by the -T designation.

2. Devices may also be marked with full part number: 811L, 812M etc. XX refers to lot.

# Absolute Maximum Ratings

#### Pin Terminal Voltage with Respect to Ground

| V <sub>CC</sub>                                             | -0.3V to 6.0V                     |

|-------------------------------------------------------------|-----------------------------------|

| RESET, $\overline{\text{RESET}}$ and $\overline{\text{MR}}$ | -0.3V to (V <sub>CC</sub> + 0.3V) |

| Input Current at $V_{CC}$ and $\overline{MR}$               | 20mA                              |

| Output Current: RESET or RESET                              | 20mA                              |

| Rate of Rise at V <sub>CC</sub>                             | 100V/µs                           |

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolonged time periods may affect device reliability

| Power Dissipation ( $T_A = 70^{\circ}C$ ) | 20mW          |

|-------------------------------------------|---------------|

| (Derate SOT-143 4mW/°C above 70°C)        |               |

| Operating Temperature Range               | 40°C to 105°C |

| Storage Temperature Range                 | 65°C to 160°C |

| Lead Temperature (soldering, 10 sec)3     | 00°C          |

# **Electrical Characteristics**

Unless otherwise noted V<sub>CC</sub> is over the full voltage range,  $T_A = -40^{\circ}$ C to 105°C.

Typical values at  $T_A = 25^{\circ}$ C,  $V_{CC} = 5$ V for L/M/J devices,  $V_{CC} = 3.3$ V for T/S devices and  $V_{CC} = 3$ V for R devices.

| Parameter                              | Symbol            | Conditions                                                                                                                                                                                                        |                                                                                                                                                                  | Min                  | Тур    | Max                       | Units  |

|----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|---------------------------|--------|

| Input Voltage (V <sub>CC</sub> ) Range | V <sub>CC</sub>   | $T_A = 0^{\circ}C \text{ to } 70^{\circ}C$ $T_A = -40^{\circ}C \text{ to } 105^{\circ}C$                                                                                                                          |                                                                                                                                                                  | 1.1<br>1.2           |        | 5.5<br>5.5                | V      |

| Supply Current (Unloaded)              | I <sub>CC</sub>   | $ \begin{array}{l} T_{A} = -40^{\circ} C \ to \ 85^{\circ} C \\ T_{A} = -40^{\circ} C \ to \ 85^{\circ} C \\ T_{A} = 85^{\circ} C \ to \ 105^{\circ} C \\ T_{A} = 85^{\circ} C \ to \ 105^{\circ} C \end{array} $ | $\label{eq:V_CC} \begin{array}{l} V_{CC} < 5.5V, \ L/M/J \\ V_{CC} < 3.6V, \ R/S/T \\ V_{CC} < 5.5V, \ L/M/J \\ V_{CC} < 3.6V, \ R/S/T \end{array}$              |                      | 6<br>5 | 15<br>10<br>25<br>20      | μA     |

| Reset Threshold                        | V <sub>TH</sub>   | L devices                                                                                                                                                                                                         | $T_A = 25^{\circ}C$<br>$T_A = -40^{\circ}C \text{ to } 85^{\circ}C$<br>$T_A = 85^{\circ}C \text{ to } 105^{\circ}C$                                              | 4.56<br>4.50<br>4.40 | 4.63   | 4.70<br>4.75<br>4.86      | V      |

|                                        |                   | M devices                                                                                                                                                                                                         | $T_A = 25^{\circ}C$<br>$T_A = -40^{\circ}C \text{ to } 85^{\circ}C$<br>$T_A = 85^{\circ}C \text{ to } 105^{\circ}C$                                              | 4.31<br>4.25<br>4.16 | 4.38   | 4.45<br>4.50<br>4.56      |        |

|                                        |                   | J devices                                                                                                                                                                                                         | $ \begin{array}{l} T_A = 25^\circ C \\ T_A = -40^\circ C \text{ to } 85^\circ C \\ T_A = 85^\circ C \text{ to } 105^\circ C \end{array} $                        | 3.93<br>3.89<br>3.80 | 4.00   | 4.06<br>4.10<br>4.20      |        |

|                                        |                   | T devices                                                                                                                                                                                                         | $ \begin{array}{l} T_{A} = 25^{\circ}C \\ T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C \\ T_{A} = 85^{\circ}C \text{ to } 105^{\circ}C \end{array} \end{array} $ | 3.04<br>3.00<br>2.92 | 3.08   | 3.11<br>3.15<br>3.23      |        |

|                                        |                   | S devices                                                                                                                                                                                                         | $ \begin{array}{l} T_A = 25^\circ C \\ T_A = -40^\circ C \text{ to } 85^\circ C \\ T_A = 85^\circ C \text{ to } 105^\circ C \end{array} $                        | 2.89<br>2.85<br>2.78 | 2.93   | 2.96<br>3.00<br>3.08      |        |

|                                        |                   | R devices                                                                                                                                                                                                         | $T_A = 25^{\circ}C$<br>$T_A = -40^{\circ}C \text{ to } 85^{\circ}C$<br>$T_A = 85^{\circ}C \text{ to } 105^{\circ}C$                                              | 2.59<br>2.55<br>2.50 | 2.63   | 2.66<br>2.70<br>2.76      |        |

| Reset Threshold Temp. Coefficient      | TC <sub>VTH</sub> |                                                                                                                                                                                                                   |                                                                                                                                                                  |                      | 30     |                           | ppm/°C |

| V <sub>CC</sub> to Reset Delay         |                   | $V_{CC} = V_{TH}$ to ( $V_{TH}$ - 12                                                                                                                                                                              | 5mV), L/M/J devices                                                                                                                                              |                      | 40     |                           | μs     |

|                                        |                   | $V_{CC} = V_{TH}$ to ( $V_{TH}$ - 12                                                                                                                                                                              | 5mV), R/S/T devices                                                                                                                                              |                      | 20     |                           |        |

| Reset Active Timeout Period            |                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                                                                                                                                                               |                                                                                                                                                                  | 140                  |        | 560                       | ms     |

|                                        |                   | $T_A = -40^{\circ}C$ to $105^{\circ}C$                                                                                                                                                                            |                                                                                                                                                                  | 100                  |        | 840                       |        |

| MR Minimum Pulse Width                 | t <sub>MR</sub>   |                                                                                                                                                                                                                   |                                                                                                                                                                  | 10                   |        |                           | μs     |

| MR Glitch Immunity                     |                   | Note 3                                                                                                                                                                                                            |                                                                                                                                                                  |                      | 100    |                           | ns     |

| MR to RESET Propagation Delay          | t <sub>MD</sub>   | Note 2                                                                                                                                                                                                            |                                                                                                                                                                  |                      | 0.5    |                           | μs     |

| MR Input Threshold                     | VIH               | $V_{CC} > V_{TH (MAX)}, IMP8^{-1}$                                                                                                                                                                                | 11/812L/M/J                                                                                                                                                      | 2.3                  |        | 0.0                       | V      |

|                                        | VIL               | V <sub>CC</sub> > V <sub>TH (MAX)</sub> , IMP8 <sup>-</sup>                                                                                                                                                       | 11/010D/C/T                                                                                                                                                      | 0.71/                |        | 0.8                       |        |

|                                        | V <sub>IH</sub>   | $V_{CC} > V_{TH (MAX)}$ , IIVIFO                                                                                                                                                                                  | 11/012n/3/1                                                                                                                                                      | 0.7V <sub>CC</sub>   |        | 0.25V <sub>CC</sub>       |        |

| MR Pull-up Resistance                  | VIL               |                                                                                                                                                                                                                   |                                                                                                                                                                  | 10                   | 20     | 0.23V <sub>CC</sub><br>30 | kΩ     |

| Low RESET Output Voltage (IMP811)      | V <sub>OL</sub>   | V <sub>CC</sub> = V <sub>TH</sub> min., I <sub>SINK</sub> =                                                                                                                                                       | 1 2mA IMP811R/S/T                                                                                                                                                | 10                   | 20     | 0.3                       | V      |

|                                        | *UL               | $V_{CC} = V_{TH} \text{ min., } I_{SINK} =$                                                                                                                                                                       |                                                                                                                                                                  |                      |        | 0.0                       | v      |

|                                        |                   | $V_{CC} > 1.1V, I_{SINK} = 50\mu$                                                                                                                                                                                 |                                                                                                                                                                  | -                    |        | 0.3                       |        |

| High RESET Output Voltage (IMP811)     | V <sub>OH</sub>   |                                                                                                                                                                                                                   | <sub>CE</sub> = 500µA, IMP811R/S/T                                                                                                                               | 0.8V <sub>CC</sub>   |        |                           | V      |

|                                        |                   |                                                                                                                                                                                                                   | $_{CE} = 800 \mu A$ , IMP811L/M/J                                                                                                                                | V <sub>CC</sub> -1.5 |        |                           |        |

| Low RESET Output Voltage (IMP812)      | V <sub>OL</sub>   | $V_{CC} = V_{TH} \text{ max., } I_{SIONCE} = 0.00 \text{ J} \text{ max., } IM \text{ for } 2 \text{ max.}$                                                                                                        |                                                                                                                                                                  |                      |        | 0.3                       | V      |

|                                        |                   | $V_{CC} = V_{TH}$ max., $I_{SINK} = 3.2$ mA, IMP812L/M/J                                                                                                                                                          |                                                                                                                                                                  | 1                    |        | 0.4                       |        |

| High RESET Output Voltage (IMP812)     | V <sub>OH</sub>   | $1.8V < V_{CC} < V_{TH}$ min., $I_{SOURCE} = 150\mu A$                                                                                                                                                            |                                                                                                                                                                  | 0.8V <sub>CC</sub>   |        |                           | V      |

Notes: 1. Production testing done at  $T_A = 25^{\circ}$ C. Over temperature specifications guaranteed by design only using six sigma design limits. 2.  $\overrightarrow{RESET}$  output is active LOW for the IMP811 and RESET output is active HIGH for the IMP812. 3. Glitches of 100ns or less typically will not generate a reset pulse.

# **Pin Descriptions**

| Pin Number    | Name            | Function                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                |

| 2<br>(IMP811) | RESET           | RESET is asserted LOW if $V_{CC}$ falls below the reset threshold and remains LOW for the 140ms minimum after the reset conditions are removed. In addition, RESET is active LOW as long as the manual reset is low.                                                                                                                                                                  |

| 2<br>(IMP812) | RESET           | RESET is asserted HIGH if $V_{CC}$ falls below the reset threshold and remains HIGH for the 140ms minimum after the reset conditions are removed. In addition, RESET is active HIGH as long as the manual reset is low.                                                                                                                                                               |

| 3             | MR              | Manual Reset Input. A logic LOW on $\overline{\text{MR}}$ asserts RESET. RESET remains active as long as $\overline{\text{MR}}$ is LOW and for 180ms after $\overline{\text{MR}}$ returns HIGH. The active low input has an internal 20k $\Omega$ pull-up resistor. The input should be left open if not used. It can be driven by TTL or CMOS logic or shorted to ground by a switch |

| 4             | V <sub>CC</sub> | Power supply input voltage (3.0V, 3.3V, 5.0V)                                                                                                                                                                                                                                                                                                                                         |

# **Related Products**

|                          | IMP809 | IMP810 | IMP811  | IMP812  |

|--------------------------|--------|--------|---------|---------|

| Max. Supply Current      | 15µA   | 15µA   | 15µA    | 15µA    |

| Package Pins             | 3      | 3      | 4       | 4       |

| Manual RESET input       |        |        |         |         |

| Package Type             | SOT-23 | SOT-23 | SOT-143 | SOT-143 |

| Active-HIGH RESET output |        |        |         |         |

| Active-LOW RESET output  |        |        |         |         |

#### **Detailed Description**

#### Reset Timing and Manual Reset (MR)

The reset signal is asserted–LOW for the IMP811 and HIGH for the IMP812 – when the V<sub>CC</sub> signal falls below the threshold trip voltage and remains asserted for 140ms minimum after the V<sub>CC</sub> has risen above the threshold.

A logic low on  $\overline{\text{MR}}$  asserts  $\overline{\text{RESET}}$  LOW on the IMP811 and HIGH on the IMP812.  $\overline{\text{MR}}$  is internally pulled high through a 20k $\Omega$ resistor and can be driven by TTL/CMOS gates or with open collector/drain outputs.  $\overline{\text{MR}}$  can be left open if not used.  $\overline{\text{MR}}$  may be connected to a normally-open switch connected to ground without an external debounce circuit.

For added noise rejection, a  $0.1\mu F$  capacitor from  $\overline{MR}$  to Ground can be added.

Figure 1. Reset Timing and Manual Reset (MR)

#### **Application Information**

#### **RESET Output Operation**

In  $\mu P/\mu C$  systems it is important to have the processor begin operation from a known state or be able to return the system to a known state. A RESET output to a processor is provided to prevent improper operation during power supply sequencing or low voltage – brownout – conditions.

The IMP811/812 are designed to monitor the system power supply voltages and issue a RESET signal when levels are out of range. RESET outputs are guaranteed to be active for  $V_{CC}$  above 1.1V. When  $V_{CC}$  exceeds the reset threshold, an internal timer keeps RESET active for the reset timeout period, after which RESET becomes inactive (HIGH for the IMP811 and LOW for the IMP812).

If  $V_{CC}$  drops below the reset threshold, RESET automatically becomes active. Alternatively, external circuitry or a human operator can initiate this condition using the Manual Reset ( $\overline{MR}$ ) pin. There is an internal pullup on  $\overline{MR}$  so it can be left open if it is not used.  $\overline{MR}$  can be driven by TTL/CMOS logic or even an external switch, since it is already debounced. If the switch is at the end of a long cable, it might require a bypass (100nF) at the pin if noise pickup is a problem.

Six voltage thresholds are available to support 3V and 5V systems:

| Reset Threshold |             |  |

|-----------------|-------------|--|

| Suffix          | Voltage (V) |  |

| L               | 4.63        |  |

| Μ               | 4.38        |  |

| J               | 4.00        |  |

| Т               | 3.08        |  |

| S               | 2.93        |  |

| R               | 2.63        |  |

#### Valid Reset with V<sub>CC</sub> under 1.1V

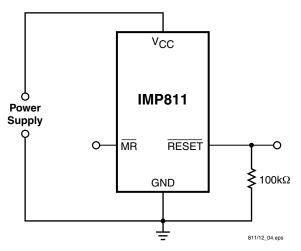

To ensure that logic inputs connected to the IMP811  $\overline{\text{RESET}}$  pin are in a known state when V<sub>CC</sub> is under 1.1V, a 100k $\Omega$  pull-down resistor at  $\overline{\text{RESET}}$  is needed. The value is not critical.

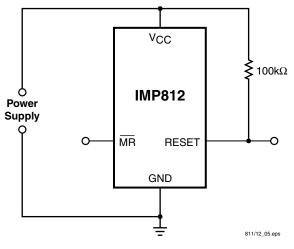

A similar pull-up resistor to  $V_{CC}$  is needed with the IMP812.

Figure 2. RESET Valid with V<sub>CC</sub> Under 1.1V

#### Negative V<sub>CC</sub> Transients

Typically short duration transients of 100mV amplitude and 20 $\mu$ s duration do not cause a false RESET. A 0.1 $\mu$ F capacitor at V<sub>CC</sub> increases transient immunity.

Figure 3. RESET Valid with V<sub>CC</sub> Under 1.1V

IMP811, IMP812

## **Application Information**

#### **Bi-directional Reset Pin Interfacing**

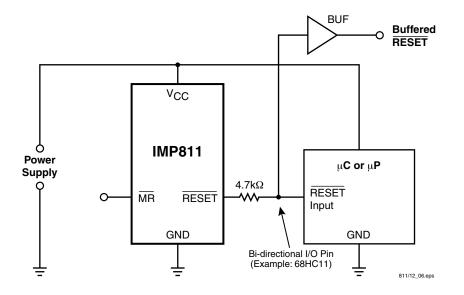

The IMP811/812 can interface with  $\mu P/\mu C$  bi-directional reset pins by connecting a 4.7k $\Omega$  resistor in series with the IMP809/810 reset output and the  $\mu P/\mu C$  bi-directional reset pin.

Figure 4. Bi-directional Reset Pin Interface

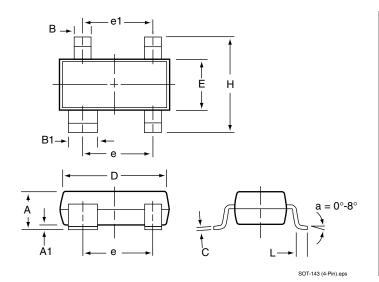

**Package Dimensions**

#### Plastic SOT-143 (4-Pin)

Inches **Millimeters** Min Max Min Max Plastic SOT-143 (4-Pin) 0.047 0.787 А 0.031 1.194 0.001 0.005 0.025 0.127 A1 В 0.014 0.022 0.356 0.559 B1 0.030 0.038 0.762 0.965 0.0034 0.006 0.086 0.152 С D 3.048 0.105 0.120 2.667 0.047 Е 0.055 1.194 1.397 е 0.070 0.080 1.778 2.032 0.071 0.079 2.007 e1 1.803 Н 2.083 0.082 0.098 2.489 0.004 0.012 0.102 0.305 L

IMP, Inc. Corporate Headquarters 2830 N. First Street San Jose, CA 95134-2071 Tel: 408-432-9100 Tel: 800-438-3722 Fax: 408-434-0335 e-mail: info@impinc.com http://www.impweb.com

© 1999 IMP, Inc. Printed in USA Publication #: 1019 Revision: A Issue Date: 08/17/99 Type: Preliminary